- 올인원 이더넷 컨트롤러 : TCP/IP, MAC & PHY 하드웨어

- 네트워크 프로토콜 완벽 내장

- 호스트 인터페이스 : 8-bit Bus 인터페이스 (Direct & Indirect)와 SPI (Serial Peripheral Interface)

- 안정적인 데이터 커뮤니케이션

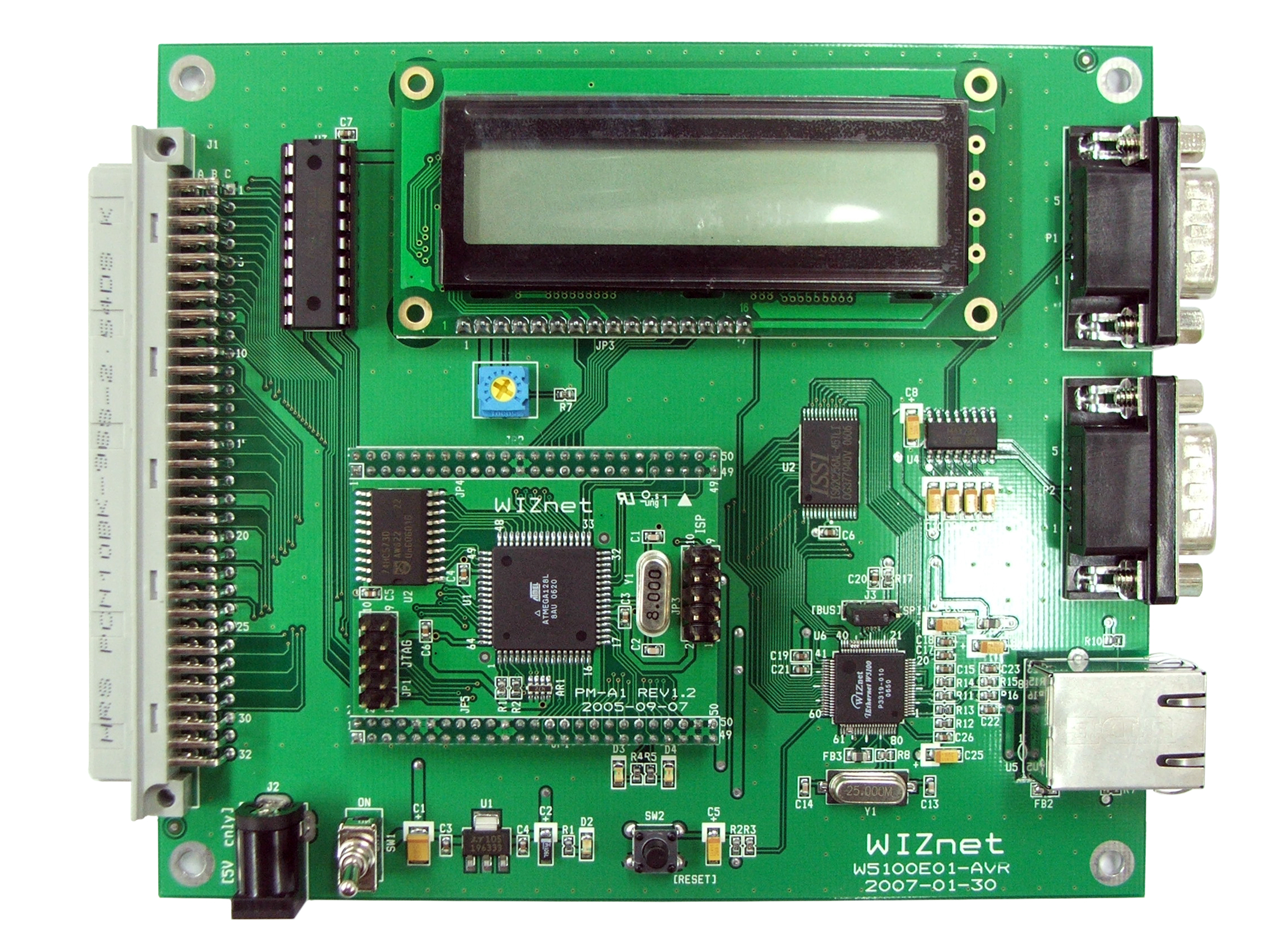

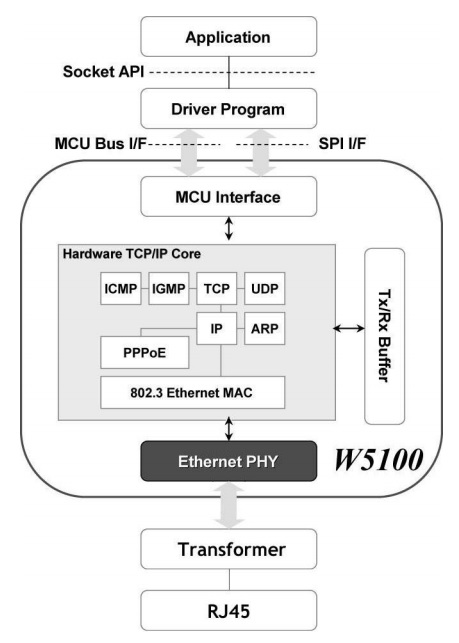

W5100은 하드웨어 방식의 TCP/IP가 내장된 이더넷 컨트롤러 칩으로 임베디드 시스템에 인터넷 연결을 쉽게 해주는 역할을 합니다. W5100은 하나의 칩에 TCP/IP 와 10/100 이더넷 MAC & PHY를 내장하고 있어, 사용자들에게 안정된 인터넷 연결을 구현 할 수 있도록 최적화 되어 있습니다. 하드웨어에 내장된 TCP/IP는 TCP, UDP, IPc4, ICMP, ARP, IGMP, PPPoE 등을 지원하며, 수년에 걸쳐 다양한 디바이스와 어플리케이션에 적용 되면서 그 기능과 성능의 안정성이 증명 되었습니다. W5100은 네트워크 패킷 송수신을 위해 16kbytes의 내장 버퍼를 지원합니다. 또한, W5100을 사용하면 복잡한 이더넷 컨트롤러를 조작하는 대신 하나의 심플한 소켓 프로그램을 사용하여 이더넷 기능을 구현 할 수 있습니다. 4개의 독립된 하드웨어 소켓을 동시에 사용 가능하며, 8-bit Bus 인터페이스(Direct & Indirect) 와 SPI(Serial Peripheral Interface)를 통하여 외장 MCU와 인터페이스 할 수 있습니다

- Hardwired TCP/IP protocols : TCP, UDP, ICMP, IPv4, ARP, IGMP, PPPoE

- Un-attackable hardware network engine for preventing network attacks such as flooding, spoofing, injection

- Host Interface : Direct/Indirect Bus & Serial Peripheral Interface (SPI MODE 0, 3)

- 4 Independent hardware socket

- Internal 16Kbytes memory for TCP/IP packet processing

- 10BaseT / 100Base TX Ethernet PHY Embedded

- Support Auto-Negotiation (Full & Half Duplex, 10 & 100 Based)

- Support Auto-MDIX

- 3.3V Operation with 5V I/O signal tolerance

- LED outputs (TX, RX, full/half duplex, Collision, link, speed)

- 80LQFP lead-free package (10x10mm)

W5100 Chip Datasheet v1.2.8

- Last Update: 2019.05.23

W5100 Chip Erratasheet v2.6

- Last Update: 2015.10.05

Limitation Note – ARP problem in the NLB environment

- Last Update: 2018.03.12

W5100 Qualification Report

- W5100 Temperature Test Report (High & Low Temperature)

- W5100 RoHS Report

W5100 Application Note

- How to implement DNS

- How to implement DHCP

- How to use Multi-casting

- How to use ADSL (PPPoE)

W5100 ioLibrary (Driver)

- W5100 Driver V1.9

W5100 Reference Schematic

- Reference Schematic (V2.1)

- W5100 Layout Guide